# D1.2 V2

# B5G Wireless Tb/s FEC KPI Requirement and Technology Gap Analysis

| Project number:            | 760150                                                                                    |

|----------------------------|-------------------------------------------------------------------------------------------|

| Project acronym:           | EPIC                                                                                      |

| Project title:             | EPIC: Enabling Practical Wireless Tb/s Communications with Next Generation Channel Coding |

| Start date of the project: | 1 <sup>st</sup> September, 2017                                                           |

| Duration:                  | 36 months                                                                                 |

| Programme:                 | H2020-ICT-2016-2                                                                          |

| Deliverable type:                             | Report                     |

|-----------------------------------------------|----------------------------|

| Deliverable reference number:                 | ICT-760150 / D1.2 / V2.0   |

| Work package contributing to the deliverable: | WP1                        |

| Due date:                                     | June 2019 – M22            |

| Actual submission date:                       | 3 <sup>rd</sup> July, 2019 |

| Responsible organisation: | IMEC          |

|---------------------------|---------------|

| Editor:                   | Claude Desset |

| Dissemination level:      | PU            |

| Revision:                 | 2.0           |

| Abstract: | To quantify the FEC improvements needed for the seven Beyond-5G Tb/s use-cases considered in EPIC, a three-step approach has been followed. First, a detailed state-of-the-art analysis of Turbo codes, LDPC codes and Polar codes has been conducted and the best implementations have been scaled to 7 nm bulk CMOS to take scaling improvements into account. Then the gap between the EPIC FEC requirements and the scaled reference designs has been assessed. Power density and energy efficiency emerge as the biggest challenges. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords: | Beyond 5G requirements, Tb/s use cases, Forward error correction, Turbo codes, LDPC codes, Polar codes, CMOS, CMOS scaling, 7 nm technology node.                                                                                                                                                                                                                                                                                                                                                                                         |

The EPIC project has received funding from the European Union's Horizon 2020 research and innovation programme under grant agreement No. 760150.

#### **Editor**

Meng Li, André Bourdoux, Claude Desset (IMEC)

**Contributors** (ordered according to beneficiary numbers)

Bianca Michal (TEC)

Onur Sahin (IDCC)

Altuğ Süral, Orhun Arpaci, Göksu Sezer, Yiğit Ertuğrul, Ertuğrul Kolağasıoğlu, Erdal Arıkan (POL)

Norbert Wehn, Claus Kestel, Matthias Herrmann, Stefan Weithoffer (TUKL)

Leefke Grosjean, Hugo Tullberg, Guido Carlo Ferrante (EAB)

Catherine Douillard, Amer Baghdadi, Charbel Abdel Nour (TB)

Jhon Jimenez (CRE)

#### **Disclaimer**

The information in this document is provided "as is", and no guarantee or warranty is given that the information is fit for any particular purpose. The content of this document reflects only the author's view – the European Commission is not responsible for any use that may be made of the information it contains. The users use the information at their sole risk and liability.

### **Executive Summary**

Future Beyond-5G use cases are expected to require wireless speeds in the Terabit/s range. This sets a number of tough challenges on the physical layer and especially on the Forward Error Correction (FEC), which is the core technology addressed by the EPIC project.

This deliverable quantifies the FEC implementation related performance improvements that the EPIC project must achieve. The global methodology in this deliverable follows three steps: defining the use cases and their requirements, describing the state-of-the-art and quantifying the gap to be bridged between requirements and current state-of-the-art.

Seven challenging Beyond-5G Terabit/s use cases are first described in detail, namely: data kiosk, virtual reality, intra-device communication, wireless fronthaul/backhaul, data centers, hybrid fiber-wireless networks, and high-throughput satellites. The main characteristics covered in this description are the system setup, the system related requirements (bit and frame error rate, throughput, latency, power, cost, flexibility) and FEC related requirements (bit and frame error rate, throughput, latency, energy efficiency, area efficiency, and power density).

Then, a comprehensive state-of-the-art search is conducted to assess the performance of leading FEC technologies with strong potential to achieve the desired requirements. The EPIC project focuses on three code classes, namely Polar Codes, Turbo Codes and Low Density Parity Check Codes. The best designs are selected as reference and their FEC performance data are scaled to the 7 nm digital bulk CMOS technology node to incorporate the improvements expected by CMOS scaling by 2020 and beyond. This allows to make a fair assessment of the different designs possible and to compare between different code classes.

Finally, the scaled state-of-the-art performance data is compared against the FEC requirements of the seven use cases to obtain the FEC performance gaps that need to be closed for the realization of the anticipated wireless Terabit/s use cases. The gap analysis has not considered the communications performance since this is not always given in implementation-oriented state-of-the-art papers.

The gap analysis shows that improvement is needed in many areas but from an implementation point of view, the biggest challenge is power consumption, hence the energy efficiency and power density. The 1 Tb/s net data throughput under a 1 GHz clock constraint is only feasible by unrolling/functional parallelism. However, unrolling under the area constraint of 10 mm² becomes only feasible for smaller block lengths and limits the number of decoding iterations. In some use cases, where the transmit power can be increased to compensate for the weakness of the FEC or the suboptimality of the decoding algorithm, this is not a challenge. Sub-microsecond latencies are also challenging. The unrolled architecture seems to be a key architecture and will need to be revisited to improve its flexibility in code rate and block length.

These performance gaps define the FEC targets for the work conducted within the EPIC project.

This document was revised after the first project review based on reviewer requirements. Modifications include an argumentation on code block length for each code family (Section 2.1), specification of code rates for each use case (Section 2.2), revision of some latency specs (Section 2.2) and prioritization of use cases for our future research (Chapter 4).

# Content

| Chapter 1    | Introduction                             | 1  |

|--------------|------------------------------------------|----|

| Chapter 2    | System and FEC KPI for Use Cases         | 3  |

| 2.1 Method   | dology                                   | 3  |

| 2.2 System   | n and FEC KPI for Use Cases              | 8  |

| 2.2.1 Data   | Kiosk                                    | 8  |

| 2.2.2 Mobi   | le Virtual Reality                       | 11 |

| 2.2.3 Wire   | less Intra-Device Communication          | 15 |

|              | less Backhaul/Fronthaul                  |    |

|              | Centers                                  |    |

|              | id Fiber-Wireless Networks               |    |

| •            | -Throughput Satellites                   |    |

|              | ısion                                    |    |

| Chapter 3    | State of the Art and Gap Analysis        | 31 |

| 3.1 Method   | dology                                   | 31 |

| 3.1.1 Scali  | ng to 7 nm CMOS Technology Node          | 31 |

| 3.1.2 Scali  | ng to the Desired Throughput             | 32 |

| 3.2 Turbo    | Codes                                    | 33 |

| 3.2.1 SoA    | of Turbo Codes                           | 33 |

| 3.2.2 Gap    | Analysis                                 | 41 |

| 3.2.3 Sum    | mary of the Gap Analysis for Turbo Codes | 48 |

| 3.3 LDPC     | Codes                                    | 48 |

| 3.3.1 SoA    | of LDPC Codes                            | 48 |

| 3.3.2 Gap    | Analysis                                 | 52 |

| 3.3.3 Sum    | mary of the Gap Analysis for LDPC Codes  | 57 |

| 3.4 Polar (  | Codes                                    | 57 |

| 3.4.1 SoA    | of Polar Codes                           | 57 |

| •            | Analysis                                 |    |

|              | mary of the Gap Analysis for Polar Codes |    |

| 3.5 Summ     | ary of the Gap Analysis for All Codes    | 67 |

| Chapter 4    | Summary and Conclusion                   | 68 |

| Chapter 5    | List of Abbreviations                    | 70 |

| Chapter 6    | Bibliography                             | 72 |

| Bibliography | <i>1</i>                                 | 72 |

# **List of Figures**

| Figure 1: Physical device illustration                                                 | 4         |

|----------------------------------------------------------------------------------------|-----------|

| Figure 2: Two possible scenarios using a data kiosk                                    | 8         |

| Figure 3: Virtual and augmented reality scenarios                                      | 11        |

| Figure 4: Communication between chips on the same device and on different device range |           |

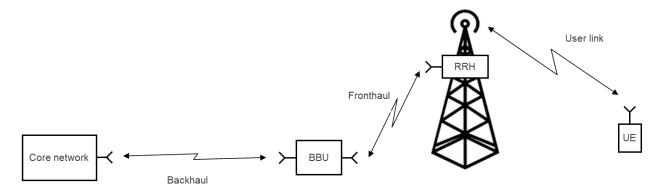

| Figure 5: Typical base station architecture with wireless fronthaul and backhaul       | 18        |

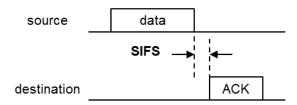

| Figure 6: Latency defined by the SIFS in IEEE 802.11ay                                 |           |

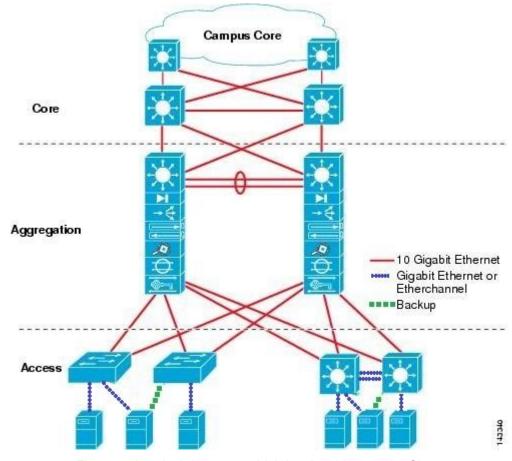

| Figure 7: A typical data centre high level architecture by Cisco                       |           |

| Figure 8: Server racks deployment and possible connectivity models                     |           |

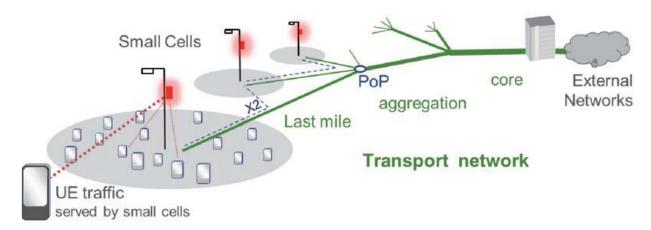

| Figure 9: Hybrid fiber-wireless links in a telecommunication transport network         | 24        |

| Figure 10: High-throughput satellite scenario                                          | 27        |

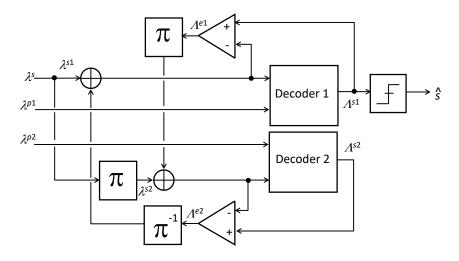

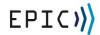

| Figure 11: Turbo decoding principle                                                    |           |

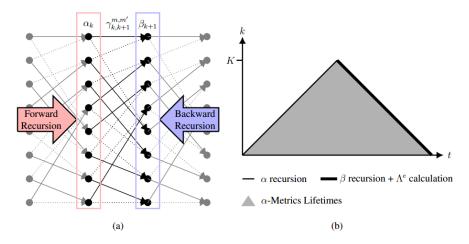

| Figure 12: State metric calculation and storage in the BCJR, Log-MAP or Max-Log-MAP    | algorithm |

| Figure 13: Sliding window principle                                                    | 36        |

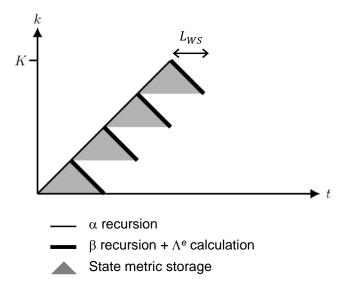

| Figure 14: PMAP architecture                                                           |           |

| Figure 15: Different XMAP schemes                                                      |           |

| Figure 16: FPMAP architecture                                                          | 39        |

| Figure 17: Hardware mappings for LDPC-BC                                               | 49        |

| Figure 18: Hardware mappings for LDPC-CC                                               | 49        |

| List of Tables Table 1: KPI explanation                                                | 3         |

| Table 2: Wafer and mask costs for different technologies                               | 4         |

| Table 3: Bounds on implementation KPI with realistic constraints                       | 8         |

| Table 4: System level KPI for the data kiosk use case                                  | 10        |

| Table 5: FEC KPI for the data kiosk use case                                           | 11        |

| Table 6: System level KPI for the virtual reality use case                             | 14        |

| Table 7: FEC KPI for the virtual reality use case                                      | 14        |

| Table 8: System level KPI for the intra-device communication use case                  | 16        |

| Table 9: FEC KPI for the intra-device communication use case                           |           |

| Table 10: System level KPI for the backhaul use case                                   | 19        |

| Table 11: System level KPI for the fronthaul use case                                  | 19        |

| Table 12: FEC KPI for the backhaul use case                                            | 20        |

| Table 13: FEC KPI for the fronthaul use case                                           | 20        |

| Table 14: System level KPI for the data center use case                                | 23        |

| Table 15: FEC KPI for the data center use case                                         |           |

| Table 16: System level KPI for the hybrid fiber-wireless networks use case             |           |

| Table 17: FEC KPI for the hybrid fiber-wireless Networks use case                      |           |

| Table 18: FEC KPI for the high-throughput satellites use case                          | 29        |

| Table 19: Summary of FEC level KPI for seven different use cases                       |           |

| Table 20: Formulas for the technology node scaling methodology                         | 32        |

| Table 22: Example of technology node scaling (hypothetical example)                                                                        | 33     |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Table 22: Comparison of SoA Turbo decoder implementations                                                                                  | 40     |

| Table 23: Comparison of SoA Turbo decoder implementations scaled to 7 nm                                                                   | 41     |

| Table 24: Comparison of SoA Turbo decoder implementations scaled to 7 nm, with clock frequencilipped to 1 GHz                              |        |

| Table 25: Gap analysis of Turbo code implementations for data kiosk use case at 7 nm                                                       | 42     |

| Table 26: Gap analysis of Turbo code implementations for virtual reality use case at 7 nm                                                  | 43     |

| Table 27: Gap analysis of Turbo code implementations for intra-device communication use ca 7 nm                                            |        |

| Table 28: Gap analysis of Turbo code implementations for backhaul use case at 7 nm                                                         | 45     |

| Table 29: Gap analysis of Turbo code implementations for fronthaul use case at 7 nm                                                        | 45     |

| Table 30: Gap analysis of Turbo code implementations for data centre use case at 7 nm                                                      | 46     |

| Table 31: Gap analysis of Turbo code implementations for hybrid fiber-wireless use case at                                                 |        |

| Table 32: Gap analysis of Turbo code implementations for high throughput satellites use case nm                                            | 47     |

| Table 33: Comparison of the actual number of processed edges of an architecture and the number of required edges for different throughputs |        |

| Table 34: Comparison of SoA LDPC-BC decoder implementations.                                                                               | 50     |

| Table 35: Comparison of SoA LDPC-BC decoder implementations scaled to a 7 nm node                                                          | 51     |

| Table 36: Comparison of SoA LDPC-CC decoder implementations.                                                                               | 52     |

| Table 37: Comparison of SoA LDPC-CC decoder implementations scaled to a 7 nm node                                                          | 52     |

| Table 38: Gap analysis of LDPC code decoder implementations for the data kiosk use case nm                                                 |        |

| Table 39: Gap analysis of LDPC code decoder implementations for the mobile virtual reality case at 7 nm.                                   | -      |

| Table 40: Gap analysis of LDPC code decoder implementations for the wireless intra-d communication use case at 7 nm.                       |        |

| Table 41: Gap analysis of LDPC code decoder implementations for the wireless backhaul use at 7 nm                                          |        |

| Table 42: Gap analysis of LDPC code decoder implementations for the wireless fronthaul use at 7 nm                                         |        |

| Table 43: Gap analysis of LDPC code decoder implementations for the data centre use case nm                                                |        |

| Table 44: Gap analysis of LDPC code decoder implementations for the hybrid fiber-wir networks use case at 7 nm                             |        |

| Table 45: Gap analysis of LDPC code decoder implementations for the high-throughput sate use case at 7 nm                                  |        |

| Table 46: The implementation details of the SoA Polar decoders                                                                             | 58     |

| Table 47: Comparison of SoA Polar decoders scaled to 7 nm                                                                                  | 60     |

| Table 48: Gap analysis of Polar code decoder implementations for data kiosk use case at 7 nr                                               | m . 62 |

| Table 49: Gap analysis of Polar code decoder implementations for virtual reality use case at                                               |        |

| Table 50: Gap analysis of Polar code decoder implementations for intra-device communicatio case at 7 nm                                    |        |

| Table 51: Gap analysis of Polar code decoder implementations for data centre use case at 7 r                                               | าm 64  |

| Table 52: Gap analysis of Polar code decoder implementations for hybrid fiber-wireless use                                                 | case   |

| at 7 nm                                                                                                                                    | 65     |

| Table 53: Gap analysis of Polar code decoder implementations for fronthaul use case at 7 nm | 65 |

|---------------------------------------------------------------------------------------------|----|

| Table 54: Gap analysis of Polar code decoder implementations for backhaul at 7 nm           | 66 |

| Table 55: Gap analysis of Polar code decoder implementations for HTS use case at 7 nm       | 66 |

## **Chapter 1** Introduction

Societal development changes how we live, work, and interact. The technical development of wireless communication systems allows us to do previously unimaginable things. For example, watching movies was previously confined in space and time, to movie theatres or living rooms and at determined times. Today we can enjoy high-quality media while on the move, anywhere and anytime, thanks to wireless mobile broadband. However, as technical possibilities develop, so do the applications. For the future, we foresee a continued increasing demand on data rates as we continue to move from standard TV to ultra-high-definition TV and virtual reality.

Forward Error Correction (FEC) is a core technology component of any digital communication system and is the enabler of practicable Beyond-5G (B5G) wireless Terabit/s (Tb/s) solutions. The main goal of EPIC is to develop a set of new implementation-ready FEC technologies that meet the cost and performance requirements of a variety of future wireless Tb/s use cases. The EPIC project puts great emphasis on evaluating the commercial viability of the project outcomes targeting B5G systems, based on a systematic idea-to-market approach as an integral part of the project execution.

In the past, steady progress in silicon technology - as predicted by Moore's law - could be counted on as the enabler of such large leaps in data rates in a few technology nodes (generations), without the need for major algorithmic innovations on the FEC design part. Indeed, already for some decades, simple technology scaling has been in effect and served as a major enabler of wireless communications at ever increasing data rates, with improved energy and area efficiency and at reduced cost. A key finding is the prediction that the upgrade to Tb/s wireless data rates will not be as smooth: the improvements carried by silicon technology progress in the next decade will significantly fall short of meeting the Tb/s FEC challenge. Moreover, FEC implementation at Tb/s will require several Tera-FLOPS of computational power, bringing forth the emergence of power density on the silicon chip as a key factor thereby adding new dimensions into the already challenging FEC design space. The EPIC project is based on the thesis that major algorithmic and architectural innovations, in an EPIC holistic design framework, will be required in the design and implementation of FEC algorithms to make wireless communications at Tb/s rates feasible. This will be applied to the three code classes considered in the EPIC project: Turbo codes, Low Density Parity Check (LDPC) codes and Polar codes, whose bit error rate (BER) performance come close to the Shannon limit.

The global methodology in this deliverable follows three steps: defining the use cases and their requirements, describing the state-of-the-art (SoA) and quantifying the gap to be bridged between requirements and current SoA.

For the first step (definition of the use cases), a review of the B5G use cases studied in current technical literature and standardization work has served as a starting point. The final choice of the use cases described in this deliverable was made based on several criteria: for the EPIC project, only use cases that directly require advances in the FEC technology are relevant. The use cases were chosen sufficiently different from each other to achieve a large diversity. The identified use cases are: data kiosk, virtual reality, intra-device communication, data centre, hybrid fiber-wireless networks, wireless fronthaul/backhaul and high-throughput satellites. Each use case offers a specific set of challenges; collectively, these use cases therefore present a diverse set of FEC design challenges. For each of the use cases, we first detail the following system level Key Performance Indicators (KPI): BER performance, throughput, latency, power consumption, cost and volume. After that, the KPI related to FEC implementation (area, area efficiency, energy efficiency and power density) are derived by scaling to different silicon technology nodes based on the power budget, cost budget and chip volume from market driven perspective for the different use cases. For silicon implementation, a realistic KPI estimation further needs to consider the practical silicon fabrication size, yield, packaging method and thermal dissipation. Hence, since

certain scaling may result in unrealistic values, we will not allow the area and power density to grow too large. We will consider the following values "within reach", although very challenging and thus deserving extensive research: target throughput from 500 Gb/s to 1000 Gb/s, latency from 0.5 ms down to 100 ns, BER from 10<sup>-6</sup> down to 10<sup>-12</sup>, area efficiency around 100 Gb/s/ mm², energy efficiency around 1 pJ/bit and power density around 0.1 W/mm². These EPIC targets represent an improvement of approximately 10x–100x in throughput, 10x–50x in energy efficiency and 3x–30x in area efficiency over the SoA. All throughput figures refer to the net data throughput (information bits) and not to the coded throughput.

For the second step (SoA), we conduct a detailed SoA search for the three code families. We review papers and references achieving the highest possible performance in terms of the KPI targeted by the EPIC project. Furthermore, we describe the key techniques and architectures used in these papers. This gives an overview of the different techniques used in the SoA and gives an indication of their suitability to reach the EPIC goals. Both generic techniques (such as parallelization, pipelining) and code specific techniques are covered.

For the third step (gap analysis), we scale the most interesting references from the SoA to the 7 nm CMOS technology node and then assess the gap between the scaled SoA and the EPIC targets. The rationale is as follows. The EPIC project objectives span the timeline of 2020 and beyond. During this timeline, the silicon technology is expected to progress to 7 nm - and possibly further - from the presently available larger technology nodes (such as 65, 40, 28 and 16 nm), hence resulting in faster digital systems and higher densities [1]. Part of the gaps to the goal of Tb/s FEC targets will be closed thanks to advances in silicon technology alone. The gaps left over after considering the advances in silicon technology are the real challenges for the EPIC project. Therefore, when analyzing the gap between the goal and the SoA, all the implementation metrics (throughput, latency, energy efficiency, area efficiency and power density) are scaled to the 7 nm technology node. Based on the International Technology Roadmap for Semiconductors (ITRS) roadmap [2] and NVIDIA study on future exascale computing [3], we estimated that moving one architecture from 28 nm to 7 nm technology will bring, approximately, a factor x12 reduction in area, a factor x4 improvement in energy efficiency and a factor x3 increase in clock speed (maximum operating frequency) but with a limitation of 1 GHz clock frequency. The scaling factors derived from these values will be used to compute the performance improvements when scaling from any technology node to 7 nm.

This deliverable is organized as follows. In Chapter 2, we give an in-depth description of each use case including all system level KPI and FEC KPI. In Chapter 3, the SoA of high speed decoders and the gap analysis between SoA and target KPI of the seven use cases for the three different code families are detailed. Chapter 4 provides a summary as well as concluding remarks.

## **Chapter 2** System and FEC KPI for Use Cases

In this chapter, we list seven B5G use cases that we have identified as being particularly interesting in the context of new FEC technologies, together with important performance targets. They are: data kiosk, virtual reality, intra-device communication, wireless fronthaul/backhaul, data centers, hybrid fiber-wireless networks, and high-throughput satellites. Each of the use cases is described with respect to the system setup, the system related requirements (BER/FER, throughput, latency, power, cost, flexibility), which are related to FEC design and implementation specification and FEC related KPI (BER/FER, throughput, latency, energy efficiency, area efficiency and power density). The deep scaled CMOS technology node brings significant implementation performance gain, e.g. the clock rate is increasing approximately 1.3 times for every technology node. Taking this important aspect into account, the FEC level KPI are listed under 3 different technology nodes (28 nm, 16 nm and 7 nm). The 10 nm is the intermediate technology node hence is not included in the tables of this chapter. After the analysis of the use cases with an emphasis on the FEC related requirements, it is possible to distinguish different types of use cases, thus, allowing us to categorize and then steer our efforts in the following work.

#### 2.1 Methodology

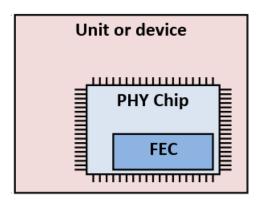

As of today, there are no wireless systems targeting a throughput of 1 Tb/s. Deriving the FEC level KPI for the seven use cases listed here is therefore a challenging task. Here, we take a top down method: The FEC is a key component of the physical layer (PHY) chip of a communication device. Parameters such as size, energy consumption, etc. of the FEC are therefore tightly connected to the parameters of the PHY chip, including cost. Using this connection, the FEC parameters such as area efficiency, energy efficiency and power density can be derived. The method is described as follows:

#### a) System level KPI determination

The system level KPI: BER/FER, latency, throughput, power consumption, cost and flexibility in code length and code rate are either obtained based on standards [4] [5] or estimated based on results in the literature.

#### b) FEC level KPI extrapolation

The FEC level KPI are: BER, latency, throughput, area efficiency, energy efficiency, power density, and flexibility in code length and code rate.

| Name of KPI       | Unit                 | Explanation                                       |

|-------------------|----------------------|---------------------------------------------------|

| Throughput        | Gb/s                 | The net information throughput.                   |

| Area              | mm <sup>2</sup>      | Area of the decoder circuit.                      |

| Power             | Watt                 | Total power dissipation by the decoder circuit.   |

| Area Efficiency   | Gb/s/mm <sup>2</sup> | Throughput per unit area.                         |

| Power Density     | W/mm <sup>2</sup>    | Power dissipation per unit area.                  |

| Energy Efficiency | pJ/bit               | Energy required for decoding one information bit. |

| Latency           | μs/ms/ns             | Duration of decoding one codeword.                |

| Frequency         | MHz                  | Achievable clock frequency of the decoder.        |

Table 1: KPI explanation

Let us first introduce the following notation:

- The cost of the whole device C<sub>unit</sub>.

- The percentage of the device cost assigned to the PHY X<sub>PHY</sub>.

- The percentage of the PHY cost assigned to the FEC X<sub>FEC</sub>.

- The power consumption of the whole device  $P_{\text{unit}}$ .

- The percentage of the power consumption of the device given to the PHY  $Y_{PHY}$ .

- The percentage of the power consumption of the PHY given to the FEC Y<sub>FEC</sub>.

- The expected number of devices initially sold (volume).

- The throughput on FEC level (same as on system level).

The FEC level cost and power budget can be obtained from equations (2.1) and (2.2).

$$FEC_{\text{cost}} = C_{\text{unit}} X_{\text{PHY}} X_{\text{FEC}}$$

(2.1)

$$FEC_{power} = P_{unit} Y_{PHY} Y_{FEC}$$

(2.2)

Figure 1: Physical device illustration

$$FEC\_chip\_area = \left(FEC_{cost} - \frac{mask\_price}{volume}\right) * wafer\_area/wafer\_price$$

(2.3)

The total chip cost consists of the die cost, the packaging and testing cost. Furthermore, it largely depends on the yield. In the following we assume that the die cost is the dominant cost part. The die cost is composed of wafer and mask cost. The wafer price is more foundry independent while the mask set price differs a lot from different foundries. The wafer and mask cost we used in EPIC is shown in Table 2. Based on the above assumption, the FEC area under different technology node with the cost limitation can be derived from equation (2.3).

| Node                 | 28 nm | 16 nm | 7 nm  |

|----------------------|-------|-------|-------|

| Wafer size (diam)    | 12"   | 12"   | 12"   |

| Full mask set price* | €1.5M | €3.2M | €6.5M |

| Wafer price*         | €5k   | €11k  | €22k  |

Table 2: Wafer and mask costs for different technologies

The other FEC level related KPI can be derived from system level KPI as follows:

Area efficiency =

$$\frac{\text{Throughpout}}{\text{FEC\_chip\_area}}$$

(bit/s/mm<sup>2</sup>) (2.4)

Energy efficiency =

$$\frac{FEC_{\text{power}}}{\text{Throughput}}$$

(pJ/bit) (2.5)

Power density =

$$\frac{FEC_{power}}{FEC_{chip\_area}}$$

(W/mm<sup>2</sup>) (2.6)

#### c) Code length selection

For standardized applications there are generally specific requirements on the code lengths to support. For instance, with OFDM systems it is generally more efficient to have an integer relationship between the number of sub-carriers and the code length such that code blocks are aligned to the modulation symbols. However, for the 7 use cases considered in this deliverable, the selected applications are still generic in order to derive general coding requirements and not directly related to frozen standards. Hence there are no strict requirements from that side and code length recommendations are possible within EPIC in view of other arguments. In particular, the trade-offs between coding performance (coding gain) and implementation aspects (throughput, complexity) should be considered.

Concerning this trade-off between coding performance and implementation, there are a few general trends. For instance, very short codes will be worse in coding performance while very long codes will generally suffer from a too high complexity. However, these trends are only generic and in order to propose recommended code length values, they need to be investigated within the 3 code families considered in EPIC, as each family can have a very specific behaviour as function of the code length.

For each code family, first insights on implementation aspects will guide the selection of typical lengths for which the EPIC targets in throughput and complexity are expected to be in reach. Additionally, error rate simulations and existing literature can be used in order to check whether a sufficient coding performance is obtained for selected code lengths.

#### **Recommendations for Turbo Codes**

According to a recent survey of efficient error-correcting codes in the short frame size regime, Turbo Codes (TC) are known to provide excellent coding gains in the moderate frame size regime (typically 150-2000 bits) and, if carefully designed, for short frame sizes as well (typically 50-150 bits) [6]. For instance, a 16-state tail-biting TC is shown to perform at 0.75 dB from Gallager's random coding bound for a frame error rate equal to 10<sup>-6</sup>.

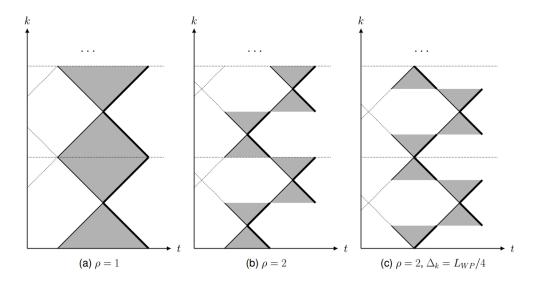

In order to achieve the EPIC goals, highly parallel architecture templates have to be investigated. Among the considered candidates, the fully pipelined iteration unrolled XMAP decoder architecture is the most promising one. With this architecture, the serial MAP decoding of complete frames is functionally parallelized. For such a decoder, the size of the pipelines grows quadratically with the size of the input frame, which sets a complexity limit on the manageable frame sizes in the order of a few hundreds of bits.

The first investigated architectures will target fixed frame sizes. However, some flexibility in this regard can be introduced. To allow efficient flexible implementations, an overlap between the different interleavers corresponding to the different sizes is desired, resulting in more regular connections and less multiplexing between different frame size configurations. The Almost Regular Permutation (ARP) interleaver template [7, 8] is able to provide these features while keeping the error correction performance close to the finite-length coding bounds. Some frame size flexibility (from a few tens up to a few hundreds of bits) can then be achieved at the price of a tolerable overhead.

However, for such frame sizes, the code is not able to perform close to the channel capacity, which can only be approached for very long data frames. The theoretical error correction performance loss for the transmission of frames of 100 information bits is around 2 dBs in the AWGN channel and it is necessary to reach a size of 1000 bits so that the loss becomes less than 1dB [9].

In order to increase the frame size, a particular form of spatial coupling can be introduced in the TC scheme by slightly modifying the ARP interleaver model so that it has some properties similar to the well-known convolutional interleaver [10]. With this kind of interleaver, the existing TC decoder architecture could be used to decode longer frames with minor modifications. Frame sizes up to a few thousand bits will then be possible.

In conclusion, use cases requiring short to medium frame sizes, from a few tens of bits up to several thousands of bits, will be targeted for TCs. TCs are also particularly well suited to use cases where flexibility is required. The code rate flexibility is not an issue for TCs, since ARP interleavers allow rate-compatible punctured TCs with very low error floors to be designed.

#### **Recommendations for LDPC codes**

In EPIC we classify block lengths of LDPC codes into three categories: moderate block lengths i.e. 800-2k bits, long block lengths, i.e. 2k-8k bits, and ultra-long block lengths, i.e. 8k-100k bits. Smaller code block sizes (e.g. 128 bit) are not considered, since in this domain LDPC codes are clearly outperformed by Turbo codes [11].

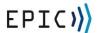

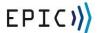

For moderate and long block sizes, we focus on quasi-cyclic LDPC block codes, since they support efficient implementation and have been shown to achieve good performance in a variety of settings. Moderate and long block lengths are long enough to allow for good communications performance while still short enough to allow for an efficient block decoder implementation with high throughput. To achieve 1 Tb/s throughput under 1 GHz frequency constraint, at least 1000 bits need to be processed in one clock cycle resulting in a huge parallelism requirement. Depending on the block length different degrees of decoding parallelism, and thus different decoding architectures, are required to achieve Tb/s throughput. Consequently, we employ the iteration unrolled LDPC block decoder architecture (highest degree of parallelism) for moderate block lengths and a (frame-interleaved) partial-parallel LDPC block decoder (medium degree of parallelism) for long code lengths.

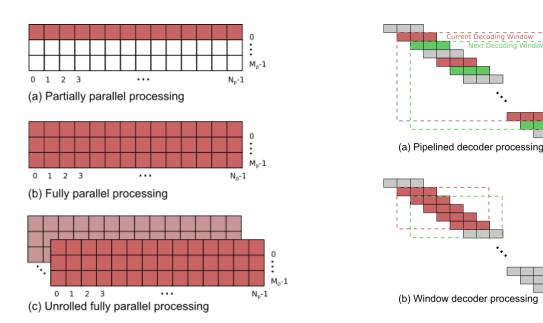

For ultra long block lengths, EPIC focuses on terminated LDPC convolutional codes (or spatially coupled LDPC codes), since they allow for hardware-efficient window decoding. The decoding complexity of the window decoder exploits the LDPC-CC's convolutional nature and allows the code length to potentially increase to infinity without affecting the hardware complexity. Multiple code rates will be supported so that the codes can be used in a variety of use-cases. For use-cases such as Data kiosk, Back/Front-haul, Intra-device communication and Data centers, code lengths in the order of N = 100k could be feasible and perhaps even suggested. This is mostly due to the high quality their corresponding wireless channels exhibit, as these consist of somewhat invariant system set-ups. Likewise, under these system conditions, the usage of code rates such as 3/4, 5/6 and 9/10 could thoroughly be achieved and even encouraged, in order to fully leverage the available bandwidth.

#### **Recommendations for Polar codes**

EPIC use cases have very demanding requirements in terms of throughput, BER and latency. There is a second set of requirements that EPIC imposes with respect to energy and area efficiency. Although EPIC does not set explicit targets for coding gains, it is clear that EPIC solutions must provide substantial coding gains to gain acceptance. In this preliminary study, we take a (1024,854) polar code as the initial starting point for polar coding solutions in EPIC (each codeword of this polar code carries 854 bits of user data in a frame of length 1024). Length 1024 is large enough to provide good coding gains. Furthermore, in earlier projects, we were able to implement this code on high-end FPGAs and achieve 100 Gb/s data throughput. We think 1 Tb/s

will be within reach using 16 nm ASIC technology. We leave the option of using longer polar codes open if the initial ASIC implementation studies suggest that length 1024 polar codes are readily implementable without violating EPIC ASIC KPIs.

We anticipate that using polar codes with block-lengths in tens of thousands will not be feasible due to the sequential nature of decoders for polar codes. The pipeline depth will grow at least linearly with the length of the code and both hardware complexity and latency will quickly exceed the EPIC constraints. As a remedy, we plan to use concatenated schemes where an outer code (such as a single-parity check (SPC) code) is combined with inner polar codes. Such an architecture will allow constructing codes with lengths in tens of thousands and provide superior coding gains. For example, one can use a two-dimensional coding scheme where 7 copies of a (1024,854) polar code are laid out as rows and a SPC code is used for computing parity bits for each column. The overall length of this code is 8192 and the rate is (5/6)\*(7/8). This type of two-dimensional coding is attractive for implementing polar codes in EPIC since decoding of the 8 rows can be carried out in parallel. If one of the eight decoders fails and means of detecting which decoder has failed is provided as part of the concatenation scheme, the SPC code can restore the data. Simulation results show that such a two-dimensional coding scheme can achieve 6 dB coding gain.

As for rate and length flexibility, the recursive u|u+v structure of polar codes can be exploited to provide some degree of flexibility. For example, the (1024,854) polar code mentioned above contains a copy of a (512,493) polar code and a copy of a (512,361) polar code. The (512,493) code in turn contains two polar codes at length 256, etc. The hardware architecture of EPIC polar encoders/decoders may mirror this recursive structure of polar codes. So, a given encoder/decoder for a polar code can be used to implement various polar codes at a set of pre-determined lengths and coding rates. In WP2, we will carry out a more detailed study of how to provide flexibility with respect to rate and code length using this approach along with concatenation.

The selected code length will follow those requirements based not so much on which of the 7 use cases is considered but rather on which of the 3 code families is investigated. On the contrary, the code rate is expected to be more specific to the different use cases. Based on different requirements in target throughput, target error rate and fluctuations of the wireless propagation, different use cases will require more or less flexibility and coding gain. Hence the suggested code rate values are discussed within the individual use cases in Section 2.2.

#### d) Data refinement with saturation based on realistic IC constraints

In some cases, the area number derived from the corresponding use case FEC cost is too large for realistic chip fabrication. This area number can exceed feasible chip area sizes that are realistic for an FEC IP on a System-on-a-Chip (SoC). Thus, we limit the maximum area for the FEC IP to a maximum of 10 mm² for all technology nodes.

FEC decoders with Tb/s throughput expected to be power-hungry. Removal of heat from the silicon surface becomes a major problem when the power density is increased further as technology scales down to deeply-scaled technology nodes such as 7 nm. Considering the thermal dissipation issue, when the power dissipation of device is around 5 Watt or more, a heat slug needs to be integrated on the Ball Grid Array (BGA). BGAs are substrate based packages where interconnection of the die to the substrate can either be made by wire bond Heat slug (HS) BGA or High performance Flip Chip (HFC) BGA:

- HS BGA ~ 5 to 6 W of thermal dissipation under natural convection

- HFC BGA ~ 6 to 8 W of thermal dissipation under natural convection

If the power dissipation exceeds the mentioned values, additional methods (e.g. heat sink / cooling fan) on system level are required. Based on the mentioned realistic area and power budget, 0.1 W/mm² is assumed as a realist power density limit. Given the assumption of an area of 10 mm² and a power density of 0.1 W/mm², a FEC decoder with 1 Tb/s throughput has a power budget of 1 Watt, an energy efficiency of 1 pJ/bit and an area efficiency of 100 Gb/s/ mm². Table 3 summarizes these implementation bounds.

| Area limit              | 10 mm²                   |

|-------------------------|--------------------------|

| Area efficiency limit   | 100 Gb/s/mm <sup>2</sup> |

| Energy efficiency limit | ~1 pJ/bit                |

| Power density limit     | 0.1 W/mm²                |

Table 3: Bounds on implementation KPI with realistic constraints

#### 2.2 System and FEC KPI for Use Cases

A review of the B5G use cases studied in current technical literature and standardization work has served as a starting point for the EPIC project. The final choice of the use cases described in this deliverable was made based on several criteria: for the EPIC project, only use cases that directly require advances in the FEC technology are relevant. Furthermore, a use case is considered viable if its implementation is expected to be feasible with improvement of current chip manufacturing technologies and production cost lies within reasonable limits. The identified use cases are: data kiosk, virtual reality, intra-device communication, data centre, hybrid fiber-wireless networks, wireless fronthaul/backhaul, and high-throughput satellites. Each use case offers a specific set of challenges; collectively, these use cases therefore present a diverse set of FEC design challenges.

#### 2.2.1 Data Kiosk

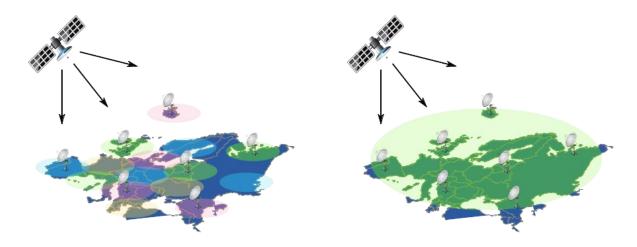

Wide coverage with high data rates has become a basic need for everyone in modern society. However, there are situations/locations where high data rates cannot be guaranteed, are simply not available, or come at a high cost. If the data to be accessed is not time-critical and can be downloaded/uploaded as a bulk, a possible solution is that the data transfer takes place at a designated station, where the user often passes by (e.g. a train station, shopping mall etc.). Such a data transfer station is called the data kiosk. We can categorize the data kiosk in two classes depending on whether the data exchange is the main reason for interacting (user connects with data kiosk for data exchange only) or whether there is another main reason (user connects with data kiosk e.g. while passing through an airport gate). The two different scenarios are illustrated in Figure 2. In both cases the user is situated in front of the machine, holding its terminal close to a marked area. However, in the first case, the time for the data exchange is not as critical as the user will not leave the data kiosk until the download is finished. In the second case as the user is not consciously connecting to the data kiosk, the data exchange should only take a very short duration of time. In the following we will focus on the second scenario.

Figure 2: Two possible scenarios using a data kiosk.

The IEEE P802.15 Working Group for Wireless Personal Area Networks studies the data kiosk use case for the amendment IEEE 802.15.3d [12] [13]. The data kiosk itself is an infra-structure product. The device it is used with (mobile phone, etc.) is however an end-user product.

#### 2.2.1.1 System Setup and Requirements

A data kiosk use case scenario has two interacting devices: The one device is the data kiosk, which is a machine installed at a fixed location with good public access, e.g. a subway station. The other device is the user terminal. Any electronic device such as mobile phones, digital cameras, computers, game devices etc. could potentially be used together with the data kiosk. However, the device needs to support wireless access, multi-stream transmission, and have sufficient processing power to allow for Tb/s throughputs.

The data kiosk is connected to the network through wired connections, allowing the transmission of high data rates without the challenges a wireless channel imposes. The connection between the user and the kiosk terminal is however wireless. The distance between the user terminal and the data kiosk is in the order of a few centimetres. There is no interference from other terminals. The wireless channel between transmitter and receiver can therefore be considered as a high-quality line-of-sight (LOS) channel which is mostly static and frequency flat [14]. But reflections can result in a more complicated channel model [13]. To achieve Tb/s throughput, the bandwidth of the transmitted signal needs to be very large. A possible candidate frequency band for the data kiosk is the 275-325 GHz frequency band [12]. The overall time during which the user terminal is connected to the data kiosk should be very short. During this time, the data kiosk needs to establish the connection, identify the user, transmit or receive the desired data, and assure that the data transfer was successful. Encryption might be relevant as well. Retransmissions in the form of HARQ can be used.

In the context of Tb/s communication, we will focus on the scenario where the user decides on initiating either a download or an upload. The traffic on the transmission link is therefore highly asymmetric. Any post-processing of the transferred data (e.g. by a video player) is done after the entire download or upload is finished. It is assumed that the user, while passing by the turnstile, is connected to the data kiosk for about 1 s. During this time depending on the channel conditions a bulk transmission of about 10-1000 Gb is expected. While the terminal is connected to the data kiosk, the terminal has only a minimal connection to other networks. This is necessary to use the full connecting capacity of the user terminal to achieve a high degree of parallelization in terms of antenna diversity.

#### 2.2.1.2 System-level KPI

The data kiosk use case has several interesting challenges: a machine like a data kiosk will only be used if it provides clear advantages. In a society, where the user is accustomed to constantly being able to stream content with almost no delay and at high data rates, heavy downloads using a data kiosk will only be accepted if they happen in the blink of an eye. Considering the scenario where the data kiosk is collocated with e.g. a train station turnstile a reasonable assumption is that user and data kiosk are connected for about 1 second.

In terms of form factor and energy consumption, the data kiosk itself has little constraints as it is installed at a fixed location and is connected to the power supply grid. If the data kiosk is colocated with another device, e.g. a turnstile, then the placement of antennas and other parts to the data kiosk may be subject to constraints. The user terminal however is a battery powered mobile device and therefore has strong constraints regarding form factor and energy consumption [14].

Accessing the memory of the user terminal at a speed of Tb/s requires very advanced processing techniques. As for the data kiosk the transmission of the data is only in bulk, the algorithms involved can work on large amounts of data with no streaming characteristic which usually allows for simpler coding algorithms that require only a low degree of flexibility. However, there is no

possibility for retransmission once the user has left the data kiosk, putting sever constraints on the BER.

| KPI                       | Value                                                                     |

|---------------------------|---------------------------------------------------------------------------|

| BER                       | < 10 <sup>-12</sup> (< 10 <sup>-14</sup> for offline decoding scenario)   |

| Latency                   | 1 s                                                                       |

| Power                     | 5 W                                                                       |

| Throughput                | 1000 Gb/s                                                                 |

| Cost                      | 500€                                                                      |

| Flexibility (coding rate) | Moderate (rate 1/2 for offline decoding; rates 3/4 to 9/10 for real-time) |

Table 4: System level KPI for the data kiosk use case

#### 2.2.1.3 FEC-level KPI

In order to determine the KPI regarding the FEC unit we use the method described in Section 2.1. As the data kiosk itself has fewer constraints on form factor etc., the analysis is based on the mobile device only. A mobile phone is used as a reference device. Here we make the assumption that, in the future, any high-end mobile phone is going to be equipped with the possibility of downloading in a "data kiosk fashion". Given the system-level discussion we set the goal to a throughput of 1000 Gb/s. Based on a recent report on the number of iPhones sold in 4<sup>th</sup> quarter during 2017 [15], we assume the volume value to be 50 million. Considering that to start with only medium to high-end mobile phones will have a data kiosk download feature, a price of 500 € is set per device. To be able to calculate the FEC cost, the physical chip cost percentage is set to 15% where 2% are reserved for the FEC. A mobile phone typically consumes 5 W where about 800 mW (~15%) are used for an active cell radio [16]. However, during the time the user and the data kiosk are connected, the cell radio can be given more power (~60%) as the time of connection is very short. Extremely low error rate transmission is expected, a significant amount (~30%) of power should therefore be given to the FEC unit.

As for the data kiosk use case bulks of data are transmitted without any streaming characteristic, latency cannot be quantified in the same sense as for the other use cases. The overall goal is to transmit as much data as possible during ~1 s. About 0.5 ms could be assigned to the FEC.

Due to the way the data is transmitted, very large block length can be considered and only a low degree of flexibility in terms of block length and code rate is necessary. The best protection (rate 1/2) may be associated to a fast transmission with offline decoding for a power-limited user device, provided the BER is low enough. A few higher coding rates will be sufficient if the propagation is good enough, enabling the system to switch to a more limited protection and hence finish the transmission faster for the end user, targeting high throughput first. Given the above assumptions, the FEC KPI target values are indicated in Table 5. The values exceeding the EPIC project targets are marked orange.

| Data kiosk                    |          |      |                     |       |            |        |            |        |            |                        |

|-------------------------------|----------|------|---------------------|-------|------------|--------|------------|--------|------------|------------------------|

| Device cost                   | 500      | €    |                     |       |            |        |            |        |            |                        |

| PHY chip cost percentage (A)  | 15       | %    |                     |       |            |        |            |        |            |                        |

| FEC cost percentage (B)       | 2        | %    |                     |       |            |        |            |        |            |                        |

| FEC cost                      | 1.5      | €    |                     |       |            |        |            |        |            |                        |

| Device power                  | 5        | W    |                     |       |            |        |            |        |            |                        |

| PHY chip power percentage (C) | 60       | %    |                     |       |            |        |            |        |            |                        |

| FEC power percentage (D)      | 30       | %    |                     |       |            |        |            |        |            |                        |

| FEC power                     | 0.9      | W    |                     |       |            |        |            |        |            |                        |

| Volume                        | 50000000 |      |                     |       | with area  |        | with area  |        | with area  |                        |

| Throughput                    | 1000     | Gbps |                     |       | limitation |        | limitation |        | limitation |                        |

|                               |          |      | Node                | 28    | 28         | 16     | 16         | 7      | 7          | nm                     |

|                               |          |      | Wafer size (diam)   | 12    | 12         | 12     | 12         | 12     | 12         | inch                   |

|                               |          |      | Full mask set price | 1.5   | 1.5        | 3.2    | 3.2        | 6.5    | 6.5        | M€                     |

|                               |          |      | Wafer price         | 5     | 5          | 11     | 11         | 22     | 22         | k€                     |

| FEC area                      | 10       |      |                     | 21.45 | 10.00      | 9.53   | 9.53       | 4.54   | 4.54       | mm²                    |

| Area efficiency               | 100      |      |                     | 46.62 | 100.00     | 104.98 | 104.98     | 220.08 | 220.08     | Gbit/s/mm <sup>2</sup> |

| Energy efficiency             | 1        |      |                     | 0.9   | 0.9        | 0.9    | 0.9        | 0.9    | 0.9        | pJ/bit                 |

| Power density                 | 0.1      |      |                     | 0.042 | 0.090      | 0.094  | 0.094      | 0.198  | 0.198      | W/mm²                  |

Table 5: FEC KPI for the data kiosk use case

#### 2.2.2 Mobile Virtual Reality

Merging the real world with the digital world is what the World Economic Forum calls the "Fourth Industrial Revolution" [17]. A cornerstone embodying this idea is the technology of virtual reality and augmented reality. Virtual Reality (VR) is a technology that generates realistic images, sounds and other sensations and thus allows the user to immerse into an entirely computer-generated virtual world. Augmented Reality (AR) is a technology that immerses a user into a partially computer-generated virtual world by overlaying the real world around the user with computer-generated information. The real world is thus 'augmented' by virtual content. For both technologies, the immersion of the user can be achieved in different ways, including, for instance mobile phones, tablet PCs, eyeglasses, contact lenses, head-up displays etc. The most promising technologies in terms of experience so far involve a head-mounted display (e.g. the Gear VR, the Hololens, or the Oculus Go). Mobile VR/AR is an extension of AR and VR with the additional requirements that the application should run and be displayed on a mobile or a wearable device and that the application should allow real-time interaction [18].

Figure 3: Virtual and augmented reality scenarios

The applications of virtual and augmented reality are wide, ranging from very basic display of information or movies on glasses, to very advanced systems involving a complex virtual layer for high-speed interactive tasks. VR and AR are therefore interesting for applications in e.g. tourism (experience a helicopter flight around New York City), education (medical students performing surgeries in VR), gaming (e.g. Pokémon Go), marketing, sports coaching, and many more. In their current form, VR and AR technologies are however not satisfactory for complex applications as the

available headsets cut off the user from their surroundings, hinder mobility, and cause nausea for some users. The performance is expected to be improved significantly with the advent of 5G but for an excellent user experience transmission-, processing- and coding-techniques beyond 5G are necessary. In the following we will focus on VR.

#### 2.2.2.1 System setup and requirements

A mobile VR system consists of both an input and an output system. Although VR could theoretically interact with all five human senses, most applications consider fewer senses. Typically, cameras, accelerometers, a microphone, a GPS, etc. provide the information for the input system allowing the system to perceive orientation, acceleration, location, motion etc. as well as both audio and video. Usually, some form of command input is accepted. The output system involves both the display and audio.

In the context of the EPIC project we are interested in very advanced VR systems that solve the problems of current VR applications concerning, for instance, discomfort and nausea caused by delay, too low resolution etc. For an advanced user experience the requirements on the system are high in many aspects. These include an extreme pixel quantity and quality, as the screen is very close to the eyes. A full 360-degree spherical view that allows the user to steer his/her view by moving both head and body. A stereoscopic display should allow for 3D vision. Moreover, the resolution of the audio should be up to human hearing capabilities and furthermore audio should be reproduced with 3D fidelity. Precise motion tracking is necessary for all the above.

Achieving all these aspects simultaneously is extremely challenging in that it involves massive data transmission and processing. Consequently, one major concern for mobile VR systems is delay. Many different types of delays are present in a VR setup, including sensor delays, network delays and rendering delays. While sensor delays have been reduced to an amount that is imperceptible to humans [19], many non-sensor-specific delays remain: most importantly, the motion-to-photon latency [20], which is defined as the time interval between a user's physical motion (e.g. rotating the head) and the resulting update of a new frame presented on the display due to the motion. It is commonly assumed that for an acceptable VR experience the motion-to-photon latency should not exceed 60 ms [21]. However, humans start noticing lag at 13 ms [22]. Therefore, the latency should ideally be below 13 ms to be imperceptible. If the motion-to-photon latency is too high, the user experiences simulator sickness [23].

Another source of user discomfort is the Frames Per Second (FPS) rate, referring to the number of unique images shown per second of video. Regular video for film and television is usually played back at 30 FPS. This works for moderate-speed motion. For high-speed immersive experiences such as games, sports etc. video rates of 60 or even 120 FPS are needed to avoid motion blur and disorientation [24] (Current VR devices such as the HTC Vive Desire support 90 FPS).

With the above assumptions, an estimate of the data to be transmitted can be calculated as follows: Within the foveal field of view of a human, our eyes can detect fine-grained dots with a resolution of approximately 200 distinct dots per (angular) degree [25]. A reasonable estimate of how many pixels per degree this amounts to is 200 [24]. By shifting our eyes mechanically, without moving our head, our eyes can see at least 150 degrees horizontally and 120 degrees vertically. This amounts to  $30,000 \times 24,000 = 720$  million pixels. (If we include head movement (180 degrees) and body rotation (360 degrees), this amounts to 2.5 billion pixels for a static image.) At 36 bits/pixel this corresponds to 90 Gbits per image.

For motion video, images are flashed in a sequence. Assuming video rates of 60 FPS, the eye can receive 720 million pixels for each of the 2 eyes, at 36 bits per pixel for full colour, amounting to a total of 3.1 trillion bits/s (= 3.1 terabits/s) [24]. Today's compression algorithms can reduce the amount of data by a factor 1:300 but the remaining amount of data to be transmitted per second is still very challenging. Furthermore, it is not clear if video encoding/decoding can be carried out at such high data rates in real-time. Tb/s transmission technology reduces the need for sophisticated video compression.

Many VR devices aim at limiting the amount of data transmitted by using advanced algorithms that calculate the current image to be shown based on previous images etc. This puts a heavy burden of processing power on the head-mounted devices which can be difficult to execute given the strong limits on the form factor. An ongoing topic of research is therefore to what extent many of the calculations can be executed remotely in a cloud/server. However, remote calculations introduce additional transmission and network delays, adding to the total delay. As an alternative, we focus here on a setup where the head-mounted device has less processing power but a large memory. The images to be stored are all images that the user could possibly see by moving only the head and/or the eyes. Furthermore, a set of possible images is stored that could potentially be accessed in the very near future. As the user is moving in an entirely virtual world all these images can be pre-calculated remotely and transmitted to the VR device. The processing left for the device is then 'only' to pick the right images for the left and right eye from the database depending on the current direction and focus of the eyes. This approach shifts the burden from processing to transmission at much higher data rates and this is where a Tb/s FEC technology becomes a necessary ingredient.

For some indoor VR applications, the transmission range might only be a few meters but for outdoor applications the range could easily increase to hundred meters. Since the user is moving, the channel is neither static nor frequency flat. Moreover, if several people are using the VR application close by, interference occurs.

In general, for VR applications, the downlink channel dominates the uplink channel in terms of data rates since it involves transmitting all information for the display, meaning that the channel is bi-directional but highly asymmetric.

#### 2.2.2.2 System-level KPI

High quality VR imposes many challenges. With the estimate of 3.1 Tb/s (uncompressed) to be transmitted, the throughput is difficult to achieve. Particularly, since the operating conditions are far from simple. Due to the movement of the user, the channel conditions are in fact very challenging. Even though a line-of-sight channel might be assumed most of the time, interference from other users can significantly impair the performance.

Compression can reduce the throughput requirements but introduces latency. Additionally, compression requires computational resources and hence power. To maximize battery life-time we need to find the best trade-off between compression and transmission rate while maintaining the required quality.

Latency has a major impact on the user experience. Both the absolute latency and the latency jitter must be kept within stringent limits to keep the user experience at acceptable levels. As most of the data has to be available in real-time, retransmissions using HARQ are not admissible. On the other hand, uncoded video for purposes of VR may be more tolerable to transmission errors, which relaxes the BER requirements on the FEC subsystem.

In terms of form factor mobile VR has very strong constraints as the head-mounted devices should only weigh a few hundred grams. The devices are wireless and therefore battery mounted which imposes severe constraints on energy consumption and power density.

Due to the very different types of information transmitted, which have different delay constraints, a high degree in flexibility is necessary for the transmission and error protection. Having flexible coding rates covering the high protection region (1/2) as well as the low-protection region (such as 15/16) and multiple intermediate values will allow the system to adapt to changing propagation conditions in real-time. The lowest coding rates may come at a reduced throughput if then need to be implemented into light devices such as head-mounted displays. Flexible rate adaptation will be needed in order to adapt to changing propagation conditions.

| KPI                       | Value                    |

|---------------------------|--------------------------|

| BER                       | < 10 <sup>-6</sup>       |

| Latency                   | 13 ms                    |

| Power                     | 8 W                      |

| Throughput                | 500 Gb/s                 |

| Cost                      | 2000€                    |

| Flexibility (coding rate) | High (from 1/2 to 15/16) |

Table 6: System level KPI for the virtual reality use case

#### 2.2.2.3 FEC-level KPI

In order to determine the KPI regarding the FEC unit we use the method described in section 2.1. On system-level a BER of less than 10<sup>-4</sup> results in a quality that is rated as excellent by users [26]. For the FEC unit a BER of 10<sup>-6</sup> is targeted here. Regarding the cost of the device, a HTC VIVE Business Edition is taken as a reference which currently ranges at around 1600€. Setting the goal to developing a very advanced virtual reality device, a cost of 2000€ is assumed. Considering that 2.1 million HTC Vive devices were sold in 2016, the estimated volume is set to 2 million. 15% of the cost is assumed to be needed to develop the PHY chip and FEC is assigned about 2% of the PHY chip.

In terms of power consumption, high-end virtual reality devices like the Microsoft Hololens consume around 8 W [27]. Most of the power is taken by the display but 20% are assumed to be consumed by the PHY unit, with 15% of this being assigned to the FEC unit. The reason for the rather high PHY unit power consumption is that in the use case described here, we focus on a setup where the device has less processing capability/power but instead is equipped with a large memory and can receive and transmit significantly more data.

With a latency constraint of 13 ms at system level, an estimate on FEC level latency in the order of ~0.5 ms seems reasonable. A high degree of flexibility in terms of code rate and block length (similar to mobile phone communication) is necessary.

Given the above assumptions the FEC KPI target values are indicated in Table 7. The values exceeding the EPIC targets are marked orange.

| Virtual reality               |         |      |                     |       |            |       |            |       |            |                        |

|-------------------------------|---------|------|---------------------|-------|------------|-------|------------|-------|------------|------------------------|

| Device cost                   | 2000    | €    |                     |       |            |       |            |       |            |                        |

| PHY chip cost percentage (A)  | 15      | %    |                     |       |            |       |            |       |            |                        |

| FEC cost percentage (B)       | 2       | %    |                     |       |            |       |            |       |            |                        |

| FEC cost                      | 6       | €    |                     |       |            |       |            |       |            |                        |

| Device power                  | 8       | W    |                     |       |            |       |            |       |            |                        |

| PHY chip power percentage (C) | 20      | %    |                     |       |            |       |            |       |            |                        |

| FEC power percentage (D)      | 15      | %    |                     |       |            |       |            |       |            |                        |

| FEC power                     | 0.24    | W    |                     |       |            |       |            |       |            |                        |

| Volume                        | 2000000 |      |                     |       | with area  |       | with area  |       | with area  |                        |

| Throughput                    | 500     | Gbps |                     |       | limitation |       | limitation |       | limitation |                        |

|                               |         |      | Node                | 28    | 28         | 16    | 16         | 7     | 7          | nm                     |

|                               |         |      | Wafer size (diam)   | 12    | 12         | 12    | 12         | 12    | 12         | inch                   |

|                               |         |      | Full mask set price | 1.5   | 1.5        | 3.2   | 3.2        | 6.5   | 6.5        | M€                     |

|                               |         |      | Wafer price         | 5     | 5          | 11    | 11         | 22    | 22         | k€                     |

| FEC area                      | 10      |      |                     | 76.61 | 10.00      | 29.19 | 10.00      | 9.12  | 9.12       | mm²                    |

| Area efficiency               | 100     |      |                     | 6.53  | 50.00      | 17.13 | 50.00      | 54.82 | 54.82      | Gbit/s/mm <sup>2</sup> |

| Energy efficiency             | 1       |      |                     | 0.48  | 0.48       | 0.48  | 0.48       | 0.48  | 0.48       | pJ/bit                 |

| Power density                 | 0.1     |      |                     | 0.003 | 0.024      | 0.008 | 0.024      | 0.026 | 0.026      | W/mm²                  |

Table 7: FEC KPI for the virtual reality use case

#### 2.2.3 Wireless Intra-Device Communication

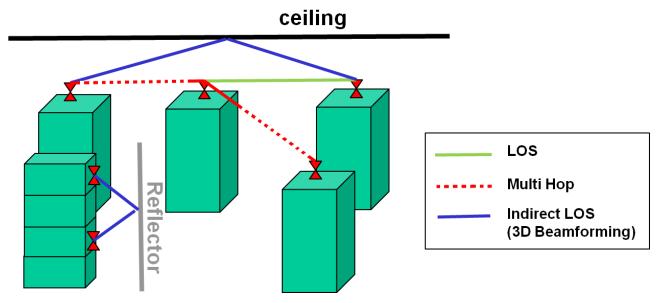

Intra-device communication (IDC) refers to communication between chips on the same Printed Circuit Board (PCB) or between chips on different PCBs in close range (approximately 1 mm up to 10 cm), as illustrated in Figure 4. Currently IDC is realized through wired buses on the PCB. If IDC is realized wirelessly instead, it will allow for reduction of pins on the integrated circuit, simplified wiring on the PCB, and easier portability. Furthermore, IDC can enable high-speed connection links between two or even more boards.

In today's communication standards such as IEEE 802.11ad [5] and IEEE 802.15.3c [28] high data rates close to 10 Gb/s are achievable. In certain applications, however, communication with even higher throughput is needed. High-speed IDC is a new territory. In the literature, it is not yet possible to find an overall system design about this subject. The operational environment of IDC is very important and detailed design work needs to be carried out according to the specific requirements of each environment.

Figure 4: Communication between chips on the same device and on different devices in close range

#### 2.2.3.1 System-level KPI

For the IDC use case, for the FEC unit we assume a BER performance around 10<sup>-12</sup>. Regarding code flexibility, we assume transmission at a fixed block length but with a code rate depending on the channel conditions.

In terms of latency we consider time frames that are already prevalent in today's PCBs as a reference. When considering the connection between CPU and Random-Access Memory (RAM), for example, information must be transferred from the RAM to the CPU in a matter of nanoseconds, whenever a corresponding request has been made by the CPU. In an *Oracle Sun Fire E25K/E20K* server, for instance, the time for a single data item to be delivered from memory to a CPU, on either the same or another PCB, lies in the range of 200-300 ns [29]. Thus, the latency for wireless IDC should not exceed this value.

When it comes to power usage, we consider the sum of the power demands of the PCB itself, together with the power required for the transceiver and its signal source, as well as the power required in order to perform the FEC. We estimate this value to be 100 W, based on the values that are stated in [30].

Data rates in today's wired IDC are up to 150 Gb/s. Any wireless IDC replacement has to support similar throughput, with possibly higher peak data rates so as to accommodate retransmissions. We quantify the target throughput for this use case with approximately 500 Gb/s.

With regards to cost and volume we estimate the device cost for a PCB with multiple chips to be approximately 200 €, based on a Xilinx Spartan 6 board, which can be found on the market with a price ranging from 50 € to 700 €. The cost of a single chip should be low, due to mass production,

and we estimate a value in the range of  $2 \in -3 \in$ , or  $4 \in$  in the worst case, respectively. As IDC is subject to mass production we consider a volume of 1 million as a reasonable number.